#### 仕 様 書

## 1. 件名

高精度クロック信号発生器の購入

## 2. 目的

本件は、国立研究開発法人量子科学技術研究開発機構(以下、「QST」という。)が運用する NanoTerasu センターにおいて、各加速周波数の基準高周波信号、ADC 用クロック信号を極低ノイズ、極低ジッタで発生させるクロック発生器、空胴 HOM 観測用切り替えスイッチ、SP4T セレクター、トリガレベル変換器を購入するものである。

#### 3. 仕様

購入品仕様は以下の通りとする。相当品可とする。

キャンドックスシステムズ製 高速デジタイザ用クロック発生器 509MHz 増設版 85SG2035C 1台

キャンドックスシステムズ製CB/SB クロック発生器 85SG28W57A1台キャンドックスシステムズ製空胴 HOM 観測用切り替えスイッチ 83SW06B141台キャンドックスシステムズ製SP4T セレクター 85KSR5A011台キャンドックスシステムズ製トリガレベル変換器 84TR03C1台※相当品の場合は以下の仕様などを満たすこと。

#### 3.1 高速デジタイザ用クロック発生器の詳細仕様

ビーム診断システムでは最大 5 GSPS の高速デジタイザを使用する機器がある。そのデジタイザに供給する 2.035 GHz 程度のクロックや 100 kHz 程度のトリガ信号を生成する必要がある。そのような信号を 508.76 MHz の基準高周波や 859.4 kHz の周回信号から生成するクロック発生器を調達すること。

#### 3.1.1 基準高周波入力

周波数: 508.76 MHz レベル: 0 dBm 程度

特性インピーダンス: 50  $\Omega$

VSWR: 1.2以下 コネクタ: SMA-F

#### 3.1.2 周回信号入力

周波数: 859.4 kHz ( = 508.76 MHz ÷ 592)

レベル: 50 Ω LVTTL

コネクタ: SMA-F

## 3.1.3 デジタイザクロック出力

周波数: 2.035 GHz ( = 508.76 MHz × [4 + N ÷ 592] )

Nの値は10程度で、ユーザ設定可能とする。( $0 \le N \le 20$ )

レベル: 0 dBm 以上、+3 dBm 以下 (50 Ω)

コネクタ: SMA-F x 2 個

ジッタ: 基準高周波入力からの増加が 100 fs 以下。

また 509MHz の遅延信号出力を 2 個、リクロックした周回信号の出力 4 個をコネクタ SMA-F で儲けること。

# 3.1.4 デジタイザトリガ出力

周波数: 859.4 kHz ÷ M

M の値は 10 程度で、ユーザ設定可能とする。(1 ≤ M ≤ 20)

N=Mのとき、この出力タイミングと基準高周波入力・デジタイザクロック出力の位相を合わせることができること。

レベル: LVTTL

パルス幅: 100 ns 程度 コネクタ: SMA-F x 2 個 ジッタ: 10 ps rms 以下

## 3.1.5 操作・表示

M, Nの値を前面LCDパネル等で表示すること。

前面パネルの押ボタンで M, Nの値を設定でき、電源を切っても保持できること。 位相リセット機能を持つこと。

## 3.1.6 外観·構造

前面パネル・背面パネルは別途指示する色で塗装すること。

前面パネル、及び、背面パネルの文字・図の表示は彫刻/スクリーン印刷を行うこと。

外観の詳細については、別途協議して決定する

寸法: EIA 19 インチラックマウント 1U、奥行き 500 mm 程度

重量: 20 kg 以下

#### 3.1.7 電源

使用電圧: AC 100 V / 200 V

入力電力: 100 VA 以下

付属品: 抜け防止 AC ケーブル (IEC C13 lock plus)

電源スイッチ: フロントパネルに設ける。 電源表示: LED(緑)で状態を表示する。

## 3.1.8 試験検査

以下の試験・検査を行い、試験検査成績書に結果を記載すること。

外観•寸法検査

寸法が規格の範囲内であること。

外観に顕著な傷がないこと。

#### 性能検査

トリガ出力: 基準高周波入力信号、周回信号入力信号を入れたときの出力波形をオシスコープで取得すること。

クロック出力: 基準高周波入力信号、周回信号入力信号を入れたときの出力波形をオシロスコープで取得すること。

各信号経路の入力-出力間の遅延時間とタイミングジッタを測定すること。

トリガ出力・クロック出力とも、信号レベル、立ち上がり・立ち下がり時間、遅延時間、タイミングジッタが仕様を満たしているか確認すること。

- 3.2. CB/SB クロック発生器の詳細仕様

- 3.2.1 外形寸法

19 インチ幅 EIA 規格 2U 高さ 奥行き 500 mm 程度

3.2.2 電源入力

電圧・周波数: AC 100 V ~ 200 V, 50/60 Hz

消費電力: 100 W以下 コネクタ: IEC-C14

ケーブル: IEC-C13 Lock Plus

3.2.3 基準高周波入力

周波数 238 MHz

入力レベル 0 dBm ± 3 dB

コネクタ SMA-female (前面)

インピーダンス  $50 \Omega$  (公称)

3.2.4 リセット入力

(1) 信号レベル LVTTL

(2) 繰り返し 60 Hz 以下

(3) コネクタ SMA-female (前面)

(4) 入力時の動作 分周器をリセットする。

## 3.2.5 基準高周波出力

周波数 2856 MHz 出力

出力数 変調・リファレンス用4(背面)、モニタ用1(前面)

出力レベル(背面変調・リファレンス用)

+12 dBm +3 dB -0 dB (MTCA. 4 DWC 2856 MHz に合わせる)

出力レベル(前面 モニタ用)

0 dBm + 3 dB - 0 dB

周波数 5712 MHz 出力

出力数変調・リファレンス用4(背面)、モニタ用1(前面)

出力レベル(背面変調・リファレンス用)

+12 dBm +3 dB -0 dB (MTCA.4 DWC 5712 MHz に合わせる)

出力レベル (前面 モニタ用)

0 dBm + 3 dB - 0 dB

コネクタ SMA-female

インピーダンス 50  $\Omega$  (公称)

出力信号の位相雑音の参考値を表1に示す。

|          | オフセット周波数   |            |             |             |

|----------|------------|------------|-------------|-------------|

| 基準高周波周波数 | 1 kHz      | 10 kHz     | 100 kHz     | 1 MHz       |

| 2856 MHz | -90 dBc/Hz | -90 dBc/Hz | -110 dBc/Hz | -125 dBc/Hz |

| 5712 MHz | -90 dBc/Hz | -90 dBc/Hz | -100 dBc/Hz | -125 dBc/Hz |

表1 出力信号の位相雑音の参考値

## 3.2.6 ADC クロック出力

周波数

238 MHz

出力数

4 (前面)

コネクタ SMA-female

インピーダンス  $50 \Omega$  (公称)

出力レベル 0 dBm + 3 dB -0 dB

位相雑音の増加量は入力の値+6 dB以下に抑えること。

## 3.2.7 IF 用基準信号出力

リセット付き分周器で 238 MHz 入力信号を 4 分周した 59.5 MHz を出力する。

周波数 59.5 MHz

出力数 4

コネクタ harlink ch1-2 (MTCA. 4 Digitizer に合わせる)

出力レベル LVDS

インピーダンス 差動平衡 100 Ω (公称)

出力信号位相雑音:位相雑音は表2に示す基準を満たすこと。

|          | オフセット周波数    |             |             |             |

|----------|-------------|-------------|-------------|-------------|

| 出力周波数    | 1 kHz       | 10 kHz      | 100 kHz     | 1 MHz       |

| 59.5 MHz | -110 dBc/Hz | -110 dBc/Hz | -110 dBc/Hz | -125 dBc/Hz |

表 2 IF 用信号の位相雑音

## 3.2.8 復調用局発信号出力:

周波数 2796.5 MHz ( = 2856 MHz - 59.5 MHz)

出力数 背面 4、前面モニタ 1

出力レベル (前面) 0 dBm +3 dB -0 dB

出力レベル (背面) +12 dBm +3 dB -0 dB

3.2.5 の基準高周波出力信号との位相関係が一意に定まっていること。

2856 MHz が-60 dBc 以下に抑制されていること。

周波数 5652.5 MHz ( = 5712 MHz - 59.5 MHz )

出力数 背面 4、前面モニタ 1

出力レベル (前面) 0 dBm +3 dB -0 dB

出力レベル (背面) +12 dBm +3 dB -0 dB

3.2.5の基準高周波出力信号との位相関係が一意に定まっていること。

5712 MHz が-60 dBc 以下に抑制されていること。

コネクタ SMA-female

出力インピーダンス 50 Ω

出力信号位相雑音位相雑音は表3に示す基準を満たすこと。

|            |            | オフセッ       | ト周波数        |             |

|------------|------------|------------|-------------|-------------|

| 復調用局発周波数   | 1 kHz      | 10 kHz     | 100 kHz     | 1 MHz       |

| 2796.5 MHz | -90 dBc/Hz | -90 dBc/Hz | -110 dBc/Hz | -125 dBc/Hz |

| 5652.5 MHz | -90 dBc/Hz | -90 dBc/Hz | -100 dBc/Hz | -125 dBc/Hz |

表3 復調用局発用信号の位相雑音

#### 3.2.9 試験検査

以下の試験を行い、試験検査成績書を提出すること。

外観試験:規定の外形寸法に収まっていること。外観に顕著な傷がないこと。入力のコネクタ数が規定の数になっていること。

電気的性能試験:出力信号の位相雑音、出力信号振幅、周波数が記載した規定を満たしていること。

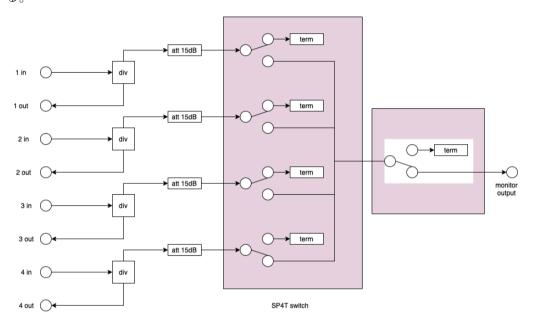

## 3.3 空胴 HOM 観測用切り替えスイッチ の詳細仕様

空胴 HOM 観測用切り替えスイッチは、509MHz の主入力信号に付随して混入している Higher

Order Mode 高周波信号を観測することを目的としている。ブロック図の例を参考図 1 に示す。 4 台の加速空胴ピックアップ信号がこのスイッチに入力される。信号は抵抗分割などの周波数特性が平坦な電力分配器に入力される。分岐信号の 1 つは、IQ 検出の目的で使用される。分岐された信号の他方の 1 つは HOM 信号観測ポートに出力される。不使用の分岐信号は 50 Q 終端する。信号の選択は手動または遠隔操作にて行う。切り替えは短時間で完了すること。切り替え時にスイッチから IQ 検出器へ反射される信号は、20dB 以上の減衰量を持つこと。各 RF ポートの VSWR は 6GHz において 1.5 以下とする。他のチャンネルとの間のアイソレーションは 40dB 以上とする。

参考図1:スイッチのブロック図

外形: EIA 19インチ幅、EIA 1U高さ、奥行き 500mm程度 RF入力:

信号レベルなど: 2MHz~6GHz 1 W以下 50 Ωインピーダンス

コネクタ: SMA-J 4個 配置: 背面パネル

VSWR: 1.5以下 @6GHz

分岐出力:

挿入損失: -9dB以下でなるべく小さいこと。4つの分岐で損失のばらつきが1dB程度以内

インピーダンス 50Ω

コネクタ: SMA-J 4個

配置:背面パネル

VSWR: 1.5以下 @6GHz

## モニタ出力:

信号レベルなど:入力の -20dB程度 50Ωインピーダンス

コネクタ: SMA-J 1個

配置:前面パネル

VSWR: 1.5以下 @6GHz

観測時以外の状態で反射を減らすために50Ω終端器を取り付けておくこと

#### 電源:

AC100V 30VA以下

## 試験検査

目視にて製作品の表面に機能上有害となる傷や歪みの無いことを確認すること。

主要寸法を所定の測定機器、測定環境にて計測して記録すること。

挿入損失、VSWR、周波数特性を測定し、結果を提出すること。

ポートの切り替えが想定通りに行われることを確認すること。

## 3.4 SP4Tセレクターの詳細仕様

フロントパネルの LED ボタンにて、入力の 4 信号から 1 信号を選択して出力するモジュールであること (参考図 2 参照)。

外形 19インチラックにマウント可能な高さ1Uであること。

周波数帯域 DC~2 GHz 以上

挿入損失は3dB以下

VSWR 1.5以下

入力4信号 コネクタ SMA-F

出力1信号 コネクタ SMA-F

フロントパネルの remote/local 切り替えにより、チェンネルの切り替えと読み出しが EtherCAT で制御可能であること。切り替え時間は100nsec 以下であること。

チャンネル間のスキューは 100psec 以下であること。

On/Off のアイソレーションは 40dB 以上であること。

AC100Vケーブルを付属すること。

前面入力、前面出力とすること。

# EtherCAT SP4T

参考図2 SP4T セレクターの参考図

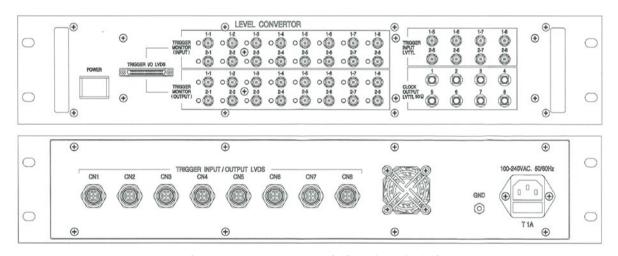

#### 3.5 トリガレベル変換器の詳細仕様

MicroTCA. 4のタイミングモジュールと組み合わせ、外部機器へタイミング信号を伝送するためのデジタル信号のレベル変換器である。

構造: 19インチラックマウント型

トリガモジュールとの入出力:VHDCI-68集合コネクタx 1 (前面パネル)

前面パネル トリガ入力: LEMO (LVTTL) x 8

前面パネル トリガ出力: LEMO (LVTTL) x 16

前面パネル クロック出力: SMA (50 Ω LVTTL) x 8

前面パネル 入力信号モニタ出力: LEMO (LVTTL) x 16

前面パネル 入出力モニタLED: 入力 x 16, 出力 x 16

背面パネル トリガ入出力: M12 X-code 4-pair (M-LVDS) x 8

## 信号系統

集合コネクタと前面・背面の入出力の間をFPGAで接続すること。

FPGA内のFan Out 及び Cross-point Switch で信号系統を制御すること。

# 信号バッファ・ドライバ

各入出力とFPGAの間に適切なバッファ・ドライバを入れること。

レベル変換器でのジッタ増加を最小限に抑えられるよう注意深く設計すること。

3.5.1 トリガモジュールとの入出力

コネクタ: 68ピン VHDCI-68 Receptacle (前面パネル)

個数: 1

信号レベル: LVDS

インピーダンス: 差動平衡100 Ω (公称)

入力信号: IN 1-1 ~ 1-8、および、IN 2-1 ~ 2-8

出力信号: OUT 1-1 ~ 1-8、および、OUT 2-1 ~ 2-8

3.5.2 前面パネル トリガ入力

コネクタ: LEMOコネクタ

信号レベル: LVTTL

インピーダンス: 1 kΩ程度

信号名: IN 1-5 ~ 1-8、および、IN 2-5 ~ 2-8の8信号。

3.5.3 前面パネル トリガ出力

コネクタ: 同軸LEMOコネクタ

信号レベル: LVTTL

インピーダンス:  $1 k \Omega$ 程度

信号名: OUT 1-1 ~ 1-8、および、OUT 2-1 ~ 2-8の16信号、

各1個を出力。

表示: 各信号にLED表示を設けること。(点灯時間100 ms程度)

3.5.4 前面パネル クロック出力

コネクタ: SMA-Jack

信号レベル: LVTTL

インピーダンス:  $50 \Omega$  (公称)

信号名: CLOCK 1 ~ 8の8信号。

3.5.5 前面パネル 入力信号のモニタ出力

コネクタ: 同軸LEMOコネクタ

信号レベル: LVTTL

インピーダンス:  $1 k \Omega$ 程度

信号名: IN 1-1 ~ 1-8、および、IN 2-1 ~ 2-8の16信号。

表示: 各信号にLED表示を設けること。(点灯時間100 ms程度)

3.5.6 背面パネル 信号入出力

入出力規格コネクタ: M12 X-Codeコネクタ

X-Code (8ピン) 1/10 Gbpsイーサネット用のものを使用し、ねじ式とすること。

IEC 61076-2-109 準拠のこと。

コネクタ名: CN 1 ~ CN 8の8個。

信号レベル: M-LVDS

インピーダンス: 差動平衡100  $\Omega$  (公称)

3.5.7 信号レベル変換

トリガモジュールからのLVDS信号入力を高速・低ジッタのバッファで受けてFPGAに入力すること。

トリガモジュールへの信号は、FPGAからの信号を高速・低ジッタのLVDSドライバで受けて 出力すること。

前面パネルからのLVTTL入力信号を高速・低ジッタのバッファで受けてFPGAに入力すること。

前面パネルへのトリガ信号出力は、FPGAからの信号を高速・低ジッタのLVTTLドライバで受けて出力すること。

前面パネルへのクロック信号出力は、FPGAからの信号を高速・低ジッタの $50\,\Omega$  LVTTLドライバで受けて出力すること。

背面パネルのM-LVDSトリガ入出力とFPGAの間を高速・低ジッタのM-LVDS Receiver / Driverで接続して入出力すること。

M-LVDSの入出力切り替えはFPGAから制御できること。

# 3.5.8 外観·構造

前面・背面パネルの外観参考図3に示す。

前面パネル・背面パネルは別途指示する色で塗装すること。

前面パネル、及び、背面パネルの文字・図の表示は彫刻/スクリーン印刷を行うこと。

寸法: EIA 19インチラックマウント 2U、奥行き500 mm程度

重量: 20 kg以下

参考図3: トリガレベル変換回路 外観参考図

#### 3.5.9 電源

使用電圧: AC 100 V / 200 V

入力電力: 100 VA以下

付属品: 抜け防止ACケーブル (IEC C13 lock plus)

電源スイッチ: フロントパネルに設ける。 電源表示: LED(緑)で状態を表示する。

## 3.5.10 試験·検査

以下の試験・検査結果を行い、試験検査成績書に結果を記載すること。

# 外観•寸法検査

寸法が規格の範囲内であること。

外観に顕著な傷がないこと。

#### 機能検査

トリガ入力が適切に認識され、トリガ出力に適切な信号が出るか確認すること。入出力が正 しく対応しているか確認すること。

トリガ入出力の LED 表示が適切であるか確認すること。

## 性能検査

トリガ出力: パルス幅 100 ns の入力信号を入れたときの出力波形をオシスコープで取得すること。

クロック出力: 100 MHz のクロックを入れたときの出力波形をオシロスコープで取得すること。

各信号経路の入力-出力間の遅延時間とタイミングジッタを測定すること。

トリガ出力・クロック出力とも、信号レベル、立ち上がり・立ち下がり時間、遅延時間、タイミングジッタが仕様を満たしているか確認すること。

## 4. 納期

令和8年2月27日

# 5. 納入場所

宮城県仙台市青葉区荒巻字青葉 468-1

NanoTerasu 内の指定する場所

## 6. 提出書類

| 書類名     | 提出時期 | 部数 |

|---------|------|----|

| 試験検査成績書 | 納入時  | 1部 |

#### (提出場所)

NanoTerasuセンター

高輝度放射光研究開発部 加速器グループ

## 7. 検査条件

第5項に示す納入場所に納入後、第6項に示す提出書類の提出と、以下の検査の合格を もって検査合格とする。

| 項目   | 内容                                |

|------|-----------------------------------|

| 員数検査 | ・員数が揃っていることを、目視により確認する。           |

| 試験検査 | ・3.1.8、3.2.9、3.3、3.5.10の試験検査成績書を提 |

|      | 出すること。                            |

# 8. 契約不適合責任

契約不適合責任については、契約条項のとおりとする。

# 9. グリーン購入法の推進

本契約において、グリーン購入法(国等による環境物品等の調達の推進等に関する法律) に適合する環境物品(事務用品、OA機器等)の採用が可能な場合は、これを採用するもの とする。

## 10. 協議

本仕様書に記載されている事項及び本仕様書に記載のない事項について疑義が生じた場合は、QSTと協議の上、その決定に従うものとする。

## (要求者)

部課室名: NanoTerasu センター

高輝度放射光研究開発部 加速器グループ

氏 名:上島 考太