# 新スーパーコンピュータ Plasma Simulatorと NECの取り組み

## The New Supercomputer 'Plasma Simulator' and NEC's Initiatives

2026年1月19日

上山根 慎

日本電気株式会社

HPC統括部

ディレクター

# 目次 Agenda

## 1. 会社紹介

Company Introduction

## 2. 新スーパーコンピュータ Plasma Simulator

New Supercomputer ‘Plasma Simulator’

## 3. NECの取り組み

NEC's Initiatives

## 4. 将来に向けて

Future Prospects

# 1. 会社紹介

## Company Introduction

# 基本情報

## Basic Information

### NEC at a Glance

設立

1899年

長年にわたる

お客さまとの信頼関係

技術力

世界

No.1

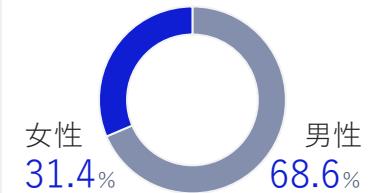

採用男女比率

※3 ※4

女性管理職比率

※5

12.8 %

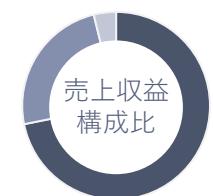

売上収益

※4

3兆 4,234 億円

ITサービス

社会インフラ

その他

特許件数

※5

約

43,000 件

研究開発費

※5

992 億円

従業員数

※5

約

10.4 万人

CDPスコア

気候変動・水セキュリティ・

サプライヤーエンゲージメント

A リスト

重大なカルテル・

談合行為の発生

※4

0 件

※1 米国国立標準技術研究所 (NIST) 主催のベンチマークテストで第1位の評価を複数回獲得

※2 NIST主催のベンチマークテストで第1位の評価を獲得 \*NISTによる評価結果は米国政府による特定のシステム、製品、サービス、企業を推奨するものではありません

※3 日本電気株式会社単体 / ※4 2025年3月期実績 / ※5 2025年3月31日現在

※6 「育児休業、介護休業等育児又は家族介護を行う労働者の福祉に関する法律」に基づく「育児休業、介護休業等育児又は家族介護を行う労働者の福祉に関する法律施行規則」71条の6第1号における育児休業等の取得割合

※7 2025年6月1日現在 障害者雇用促進法に基づく日本電気(株)、NECフレンドリースタッフ(株)、NECビジネスインテリジェンス(株)

NECグループの果たすべき役割

先進技術の実装とDXの実践により、自らを変革し続け

お客様と社会の変革をリードする存在となる

## NEC HPC事業理念

# NEC High Performance Computing Business Philosophy

科学技術の先端研究開発、および社会課題の解決に取組む大学・国研・企業の研究開発組織が、その研究開発・課題解決の効率化・加速するためのより良いプラットフォーム・サービス・SIを提供し、新たな市場の創出とHPCの適用をお客様とともに協創する。

## 科学技術の発展・深化

# 安心・安全な社会を実現するための社会課題の解決

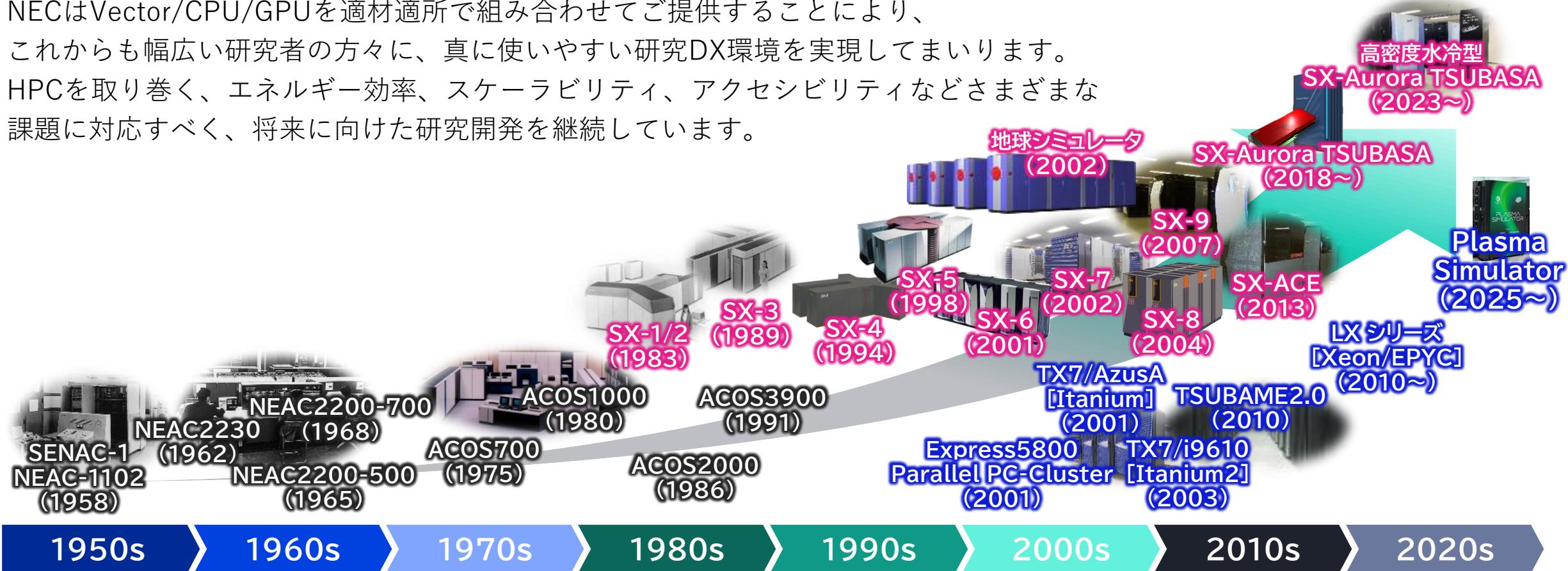

# NEC HPC製品の歩み

## History of NEC HPC Products

- NECは1958年に東北大学様との共同研究によるSENAC-1(NEAC-1102)の開発を皮切りに、日本を代表する、数多くの高性能計算システムの構築・運用支援を担当してまいりました。

- NECはVector/CPU/GPUを適材適所で組み合わせてご提供することにより、これからも幅広い研究者の方々に、真に使いやすい研究DX環境を実現してまいります。

- HPCを取り巻く、エネルギー効率、スケーラビリティ、アクセシビリティなどさまざまな課題に対応すべく、将来に向けた研究開発を継続しています。

## 2. 新スーパー コンピュータ Plasma Simulator

### The New Supercomputer ‘Plasma Simulator’

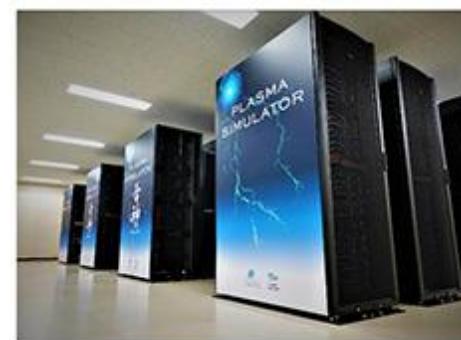

# 新スーパー コンピュータの概要

## Overview of the New Supercomputer

量子科学技術研究開発機構（QST）

六ヶ所フュージョンエネルギー研究所様

Japan Fusion Reactor

Simulator 1 (JFRS-1)

2018/6~2025/3

マシン： CRAY XC50-LC

プロセッサ： Intel Xeon Gold 6148

理論演算性能 : **4.2PFlops**

<https://www.qst.go.jp/uploaded/image/12154.jpg>

自然科学研究機構

核融合科学研究所（NIFS）様

プラズマシミュレータ

雷神

2020/7~2025/6

マシン： NEC SX-Aurora

TSUBASA A412-8

プロセッサ： NEC ベクトル

エンジン Type 10AE

理論演算性能 : **10.5PFlops**

[https://www.nifs.ac.jp/news/press-o/img/200630\\_002.png](https://www.nifs.ac.jp/news/press-o/img/200630_002.png)

## Plasma Simulator

総理論演算性能 **40.4PFlops**

旧QST機比

約10倍

旧NIFS機比

約 4倍

**旧QST機 + 旧NIFS機比 約2.7倍**

PFlops = ペタフロップス = 1秒間に1000兆回の計算ができることを表す

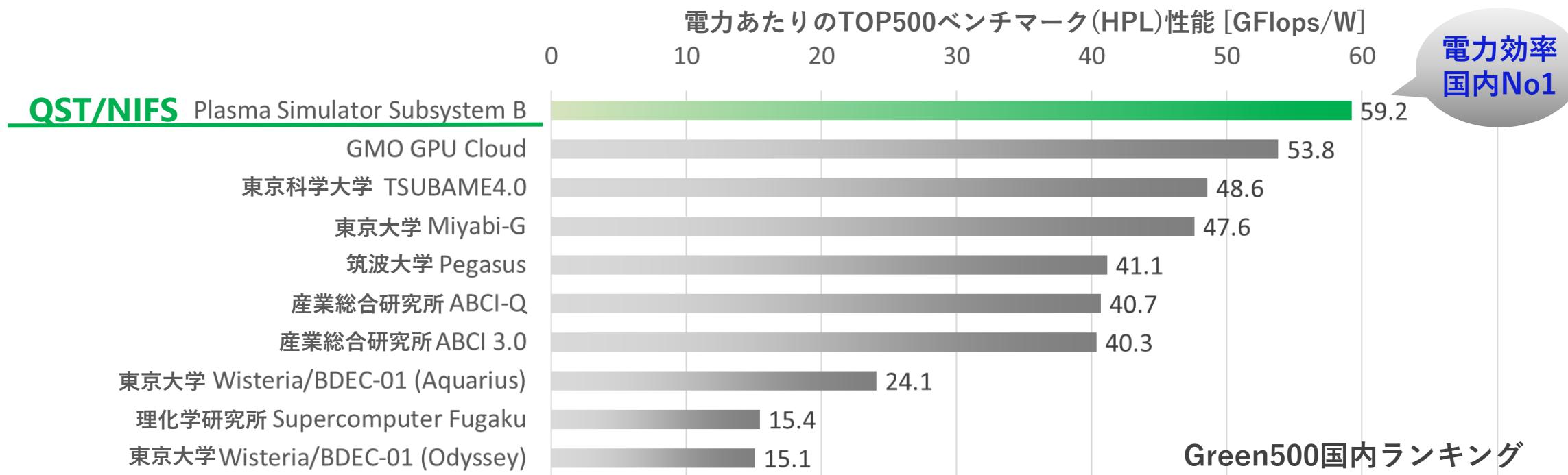

# スーパーコンピュータ電力効率：国内No.1を獲得

Achieving No.1 Power Efficiency for Supercomputers in Japan

2025年11月のGreen500リストにおいて、Plasma Simulatorが**国内1位**、**世界26位**にランクイン

## Green500 とは

- スーパーコンピュータの省エネ性能ランキング。スーパーコンピュータ性能ランキングTOP500のベンチマーク性能を消費電力で割った電力効率でランキングをするもの

- <https://www.top500.org/lists/green500/2025/11/>

## NECの貢献

大規模HPCシステム運用経験に基づき：

- TOP500ベンチマーク（HPL, High-Performance Linpack）実行時のハードウェア・ソフトウェア設定を最適化

- ベンチマーク実行時の実行パラメータの組合せをQST様/NIFS様/NECで最適化

# システム構成概略

## System Configuration Overview

**NEW**

理論演算性能:

**40.4PFlops**

### NECの取り組み

1. NECの知見を活かしたシステム提案と導入サポート

2. システム性能を最大限引き出す高速化技術

### InfiniBand Network

#### Subsystem-A CPU-HPC

360 nodes

日本初導入

Node:

2x Intel **Xeon 6980P**

768GiB **MRDIMM**

1x NDR200

**5.898 PFlops**

**270 TiB Mem.**

#### Subsystem-B APU-HPC&AI/ML

70 nodes

日本初導入

Node:

4x **AMD MI300A**

4x 128GiB HBM3

4x NDR200

**34.32 PFlops**

**35 TiB Mem.**

#### Subsystem-C CPU-Fat Memory

48 nodes

Node:

2x Intel Xeon 6544Y

**1.5TiB DDR5-5200**

1x NDR200

**0.17 PFlops**

**72 TiB Mem.**

**SSD**

**2.2PB**

For AI/ML

**HDD**

**40PB**

For HPC

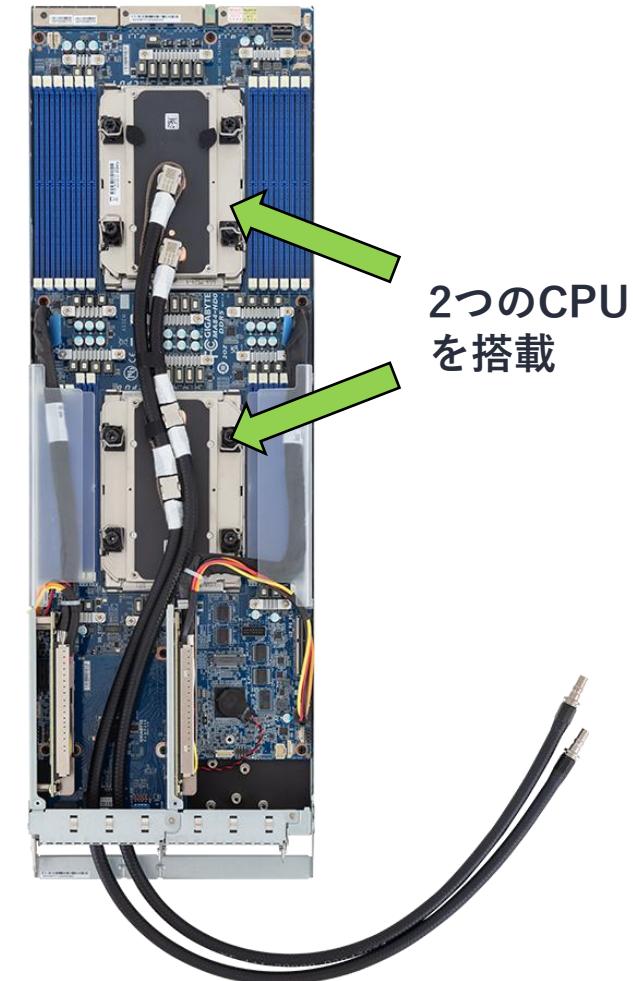

# サブシステムA

## Subsystem A

### サブシステムA (CPU-HPC)

360 nodes

Node:

2x Intel Xeon 6980P

768GiB MRDIMM-8800

1x NDR200

日本

初導入

5.898 PFlops

270 TiB Memory

|             | サブシステムA                         | JFRS-1 (2018/6~2025/3)             |

|-------------|---------------------------------|------------------------------------|

| プロセッサ       | Intel Xeon 6980P<br>2.0GHz/128c | Intel Xeon Gold 6148<br>2.4GHz/20c |

| プロセッサ数/ノード  | 2                               | 2                                  |

| コア数/ノード     | 256                             | 40                                 |

| 理論演算性能/ノード  | 16.384TF                        | 3.072TF                            |

| ノード数        | 360                             | 1370                               |

| コア数/システム    | 92,160                          | 54,800                             |

| 理論演算性能/システム | 5.898PF                         | 4.208PF                            |

| HPL性能/システム  | 5.451PF                         | 2.79PF                             |

※HPL = High Performance Linpack, TOP500でスパコンの性能を測るベンチマーク

計算ノード

<https://www.gigabyte.com/Enterprise/High-Density-Server/H374-A80-LAW1>

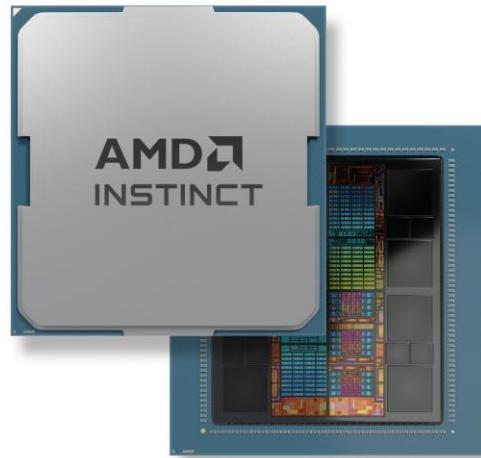

# サブシステムB

## Subsystem B

### サブシステムB (APU-HPC&AI/ML)

70 nodes

Node:

4x AMD MI300A

4x 128GiB HBM3

4x NDR200

日本

初導入

34.32 PFlops

35 TiB Memory

AMD Instinct™ MI300A アクセラレータ

<https://www.gigabyte.com/jp/Enterprise/GPU-Server/G383-R80-LAP1>

- AMDのCPU-GPU統合プロセッサ (AMD Instinct MI300A APU) を搭載

現在世界1位のスペックで採用されているプロセッサで日本初導入

- HBM3メモリによる高速メモリアクセス

- 電力あたりの性能は国内トップ

1ノードに4つの

MI300Aを搭載

# サブシステムC

## Subsystem C

### サブシステムC (CPU-Fat Memory)

48 nodes

Node:

2x Intel Xeon Gold 6544Y

**1.5TiB** DDR5-5200

1x NDR200

**0.17 PFlops**

**72 TiB Memory**

ノードあたり1.5TiB

コア当たり48GB

<https://www.gigabyte.com/jp/Enterprise/High-Density-Server/H263-S62-LAW1>

- サブシステムAで採用しているIntel Xeon 6の1つ前の世代のCPUである Intel Xeon Gold 6544Yを搭載

サブシステムAのCPU (128コア, 2.0GHz) と比較して

コア数が少なく動作周波数が高い (16コア, 3.6GHz)

- CPUコアあたりのメモリをサブシステムAの16倍搭載し、大容量メモリ

が必要な計算に対応

### 3. NECの取り組み

NEC's Initiatives

# 3-1. NECの知見を活かしたシステム提案と導入サポート

## System Proposal and Implementation Support Leveraging NEC's Expertise

- NECのトータルなコンサル力とインテグレーションで、ご要望にマッチした新システムを御提案

- 日本初採用の技術を複数導入しつつも、運用開始直後からの速やかな活用と高性能を実現

NECの強み:

- HPC分野の豊富な実績（国内・国外の大学・研究機関への導入）

- インテグレーション技術による最適なシステム設計

提供する価値:

- ユーザー目線の設計（アプリ性能・UI最適化）

- ベンダー連携（Intel/AMDとの協業による日本初導入技術）

技術差別化:

- 単なるCPU→GPU変換ではなく、「チップ特性×コード特性」に合わせた独自チューニング

- 多種多様なアーキテクチャ技術の深い知見を持つエンジニアの強み

導入サポート:

- 設置に先駆けたお客様同伴のサーバー工場見学

AMD Instinct MI300A

「HPC」で重要なメモリバンド幅とFP64性能に優れている

・今回使用するAMD Instinct MI300A（以降では「MI300A」）と、同世代のunified memory構成であるNVIDIA GH200のGPU部分を比較

- メモリバンド幅、倍精度浮動小数点型(FP64)演算性能で優位であり「HPCユーザ」に注目されている

|                             | NVIDIA GH200 GPU部分 <sup>†1</sup> | AMD Instinct MI300A GPU部分 <sup>†2</sup> | 性能比  |

|-----------------------------|----------------------------------|-----------------------------------------|------|

| 単精度ピーカ演算性能 [TFLOPS]         | 67                               | 122.6                                   | 1.82 |

| Tensor/Matrix core [TFLOPS] | 494 <sup>†3</sup>                | 122.6                                   | 0.24 |

| 倍精度ピーカ演算性能 [TFLOPS]         | 34                               | 61.3                                    | 1.80 |

| Tensor/Matrix core [TFLOPS] | 67                               | 122.6                                   | 1.82 |

| メモリバンド幅[TB/s]               | 4                                | 5.3                                     | 1.32 |

| 倍精度Byte/Flop                | 0.11                             | 0.08                                    | -    |

| TDP[W]                      | 550~760                          | 450~1,000                               | -    |

†1: <https://resources.nvidia.com/en-us/grace-cpu/grace-hopper-superchip?ncid=no-ncl>

†2: <https://www.amd.com/ja/products/accelerators/instinct/mi300/mi300a.html>

†3: FP32ではなく「TF32」という19 bit浮動小数点型

© NEC Corporation 2025

NEXT研究会<sup>†1</sup>でのノウハウ共有

## 3-2. システム性能を最大限引き出す高速化技術

### High-Speed Optimization Technologies to Maximize System Performance

- NECがHPC領域で長年培ってきたアプリケーション高速化技術を存分に活用

- GPU化に留まらない、アプリケーション特性に応じた高速化でシステムの潜在性能を最大限に発揮

技術的難易度:

- サブシステムBを構成するAMD MI300A APUの単体性能は非常に強力な一方、単にGPUへ移植しただけでは性能を引き出すことができない

- 1万を超える演算コアを満たすような超高並列化が望まれる

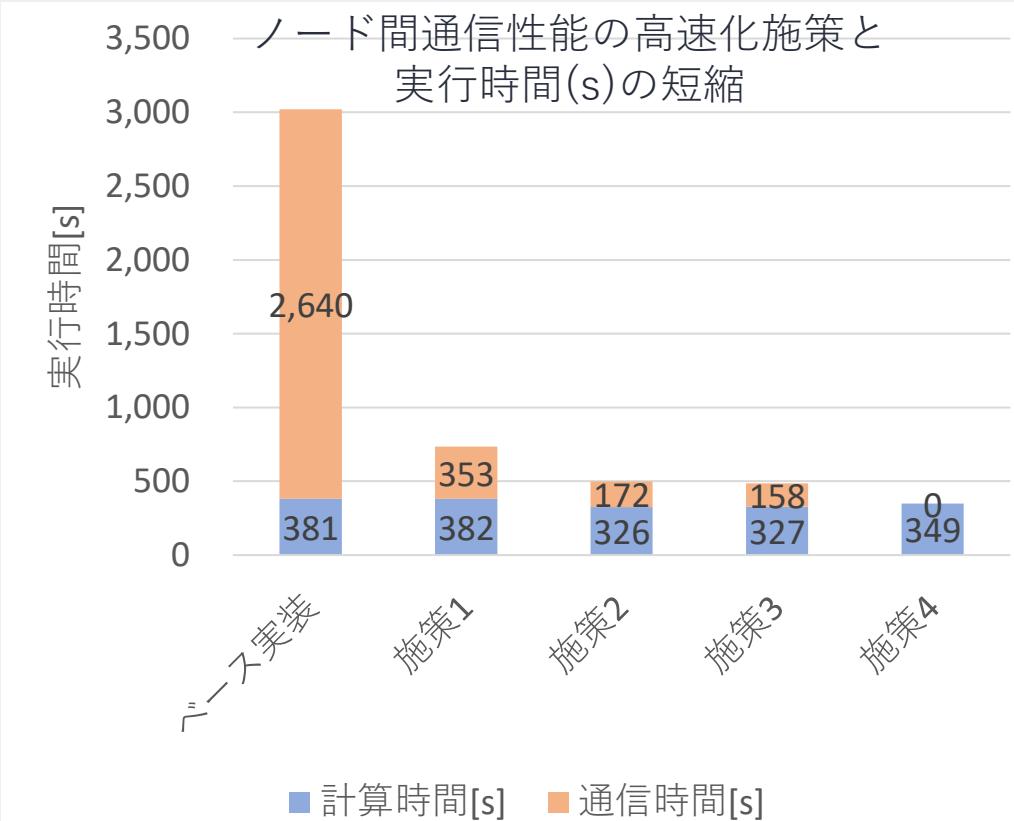

- 近年のHPCシステム全体の傾向として、圧倒的なCPU/GPU性能にノード間通信性能が追随できていない

- ノード間通信時間を短縮するための施策が重要

高速化技術の適用:

- HPC領域で長年培ってきたアプリケーション高速化技術を生かし、アプリケーションの特性に応じた高速化でシステム性能を最大限に発揮

- 右図は運用アプリケーションのひとつについて、ノード間通信時間を短縮するための施策を適用して高速化をはかった成果

## 4. 将来に向けて Future Prospects

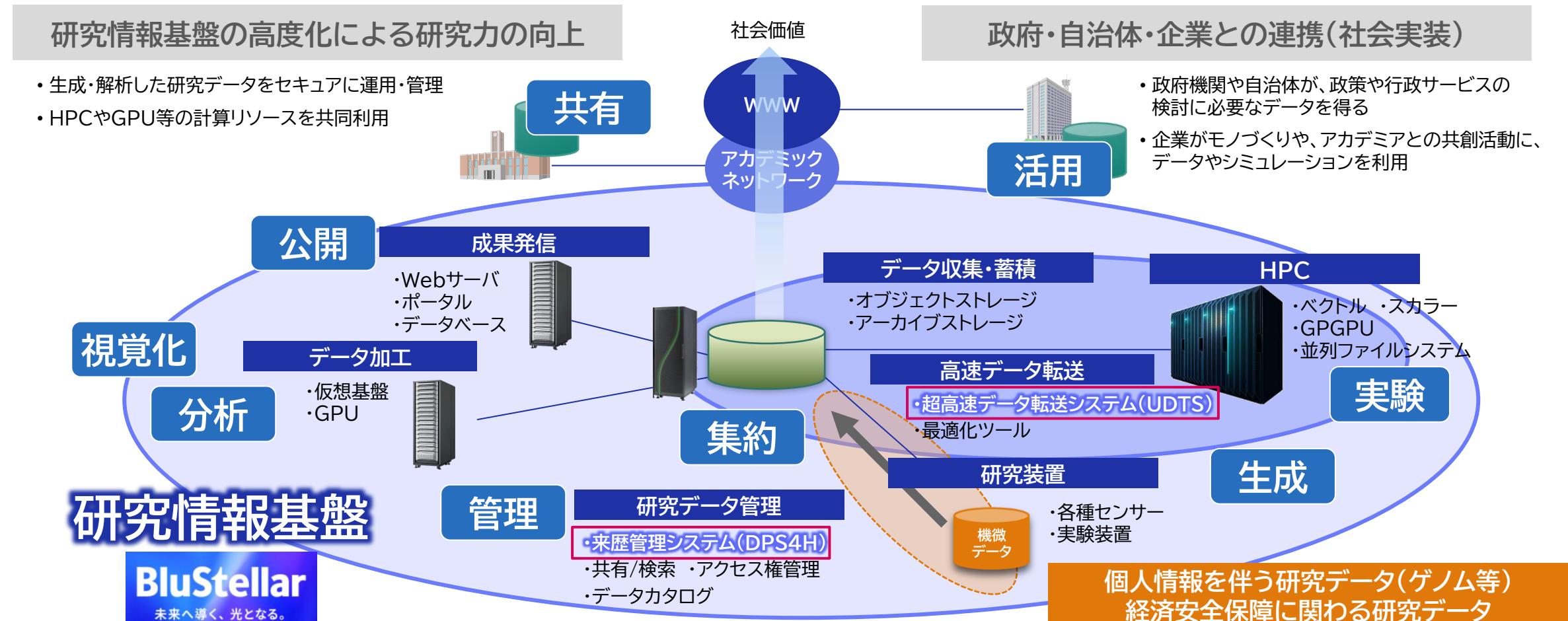

# 研究情報基盤(RII:Research Information Infrastructure) BluStellar

RII：様々な実験・設備や大規模シミュレーションから生成される大容量ファイルを集約・活用できるシステム

- ・超高速データ転送システム(UDTS)：100GbpsNW帯域“Disk-to-Disk”を超高速転送、大容量データ転送時間短縮

- ・来歴管理システム(DPS4H)：HPC研究データがいつ、誰に、どの様に生成されたか自動保存、信頼性担保

# 次世代ベクトル開発

## Next-Generation Vector Development

Next Vectorは検討中機種につき、今後構成・諸元等が変更される場合があります

■NECは欧洲Openchip社と次期ベクトルプロセッサを開発中

■新世代ベクトルプロセッサとして、Open ArchitectureであるRISC-Vをベースにベクトル機能を追加

### 開発方針

#### Open Architectureの活用

- Openかつ無償のISAで**今後の拡がり**に期待

- エコシステムを活用し、水平分業型スパコン開発が可能

#### ベクトル技術の活用

- 科学技術演算で必要な**倍精度浮動小数点演算**性能重視設計

- 演算とメモリアクセスの**バランス設計**

- 科学技術計算における**実効性能/電力**の最大化

#### 新時代のベクトルシステム

- 使いやすく**Openな利用環境**

- 高い**実効性能**と**省電力**を実現 (CPUやGPGPUスパコンシステムによる電力爆発を抑制)

### Openchip社協業

#### Openchip Software Technologies (OCT)

- RISC-VをベースにHPC/AI/ML向け**アクセラレータ**を開発

- **協業スキーム**

- NECは次世代ベクトルプロセッサを開発受託・知財提供

- RISC-V + Vector開発支援, HWライセンス提供

- コンパイラ・ライブラリ等の開発支援, ライセンス提供

- Openchip社がベクトルアクセラレータを提供, NECがシステム化・販売

#### Development

collaboration

#### Delivery

provide accelerator

Customer

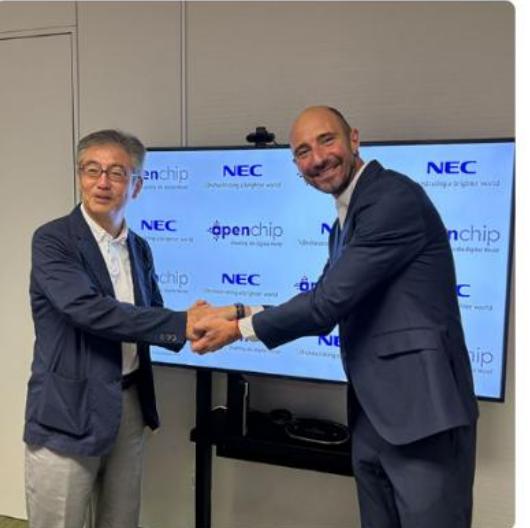

# Openchip/NEC協業のプレスリリース

## Collaboration Press Release

[openchip](#)

Enabling the Digital World

Home Openchip Solutions News Contact Work with us

### Openchip and NEC advance their collaboration on next-generation vector accelerator

PRESS RELEASE

Barcelona / Tokyo – 13 November, 2025. Openchip, a pioneering Europe-born company in the design of high-performance accelerator chips for advanced computing applications, and NEC Corporation, a global leader in IT and network technologies, announced the next stage of their strategic collaboration aimed at co-developing a next-

Check press release

## 終わりに Conclusion

NECはPlasma Simulatorシステムの安定稼働により

持続可能なエネルギー社会の実現を支援します

フュージョンエネルギーの科学的・技術的実現性の実証に向けて

High Performance Computingの力で研究開発の飛躍的加速に貢献します

**NEC**

\Orchestrating a brighter world