- 制御システムの構成

- 装置全体の運転状況を監視する

- 運転制御計算機システム

- 実験運転を円滑に行う

- 放電を手順通りに実施する

- 放電を制御する

- 放電制御計算機システム

- 電磁気データ収集計算機システム

- 高精度長時間デジタル積分器

- プラズマを制御する

- 平衡制御計算機システム

- 加熱・粒子供給制御計算機システム

- プラズマ断面位置形状実時間可視化システム

- プラントを保護する

- 保護操作

- 実験データを保存する

放電を制御する

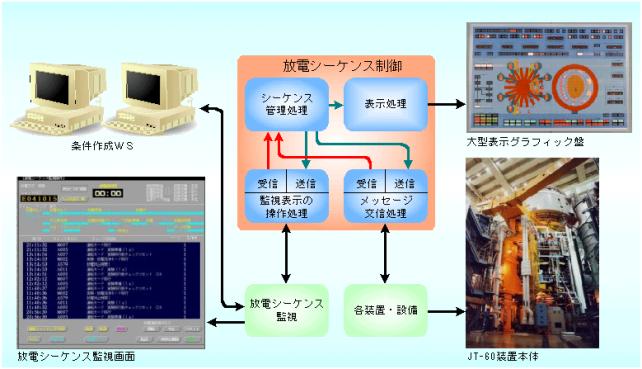

実験放電全体を司る放電シーケンス制御は、実験に関する機器に対して大きな動作の変更を管理している。放電シーケンス制御の具体的な構成要素は、以下の3つである。

(1)機器に対して指令のメッセージやタイミングパルス信号を送信し、各機器の動作完了あるいは結果を応答の形で受信し確認する、と言う指令応答。

(2)多くの指令応答の結果を入力としていろいろな論理演算が実行され、プログラムや次の指令応答が起動される一連の部分。

(3)実験運転者とのインターフェイス機能の部分で、各種操作を受け付けたり、放電シーケンスの進行状況を表示したりする。

これらの要素が上図に示すように結合動作して放電シーケンス制御が進行する。第3要素では、放電シーケンスの開始・停止操作をワークステーションのマウスにより実施でき、その後の進行の様子および動作異常の発生を放電シーケンス監視画面によって、一目で把握できる。このようにJT-60の放電シーケンスは少人数で掌握できるようになっている。これら一連の動作を担っているのが放電制御計算機システムである。

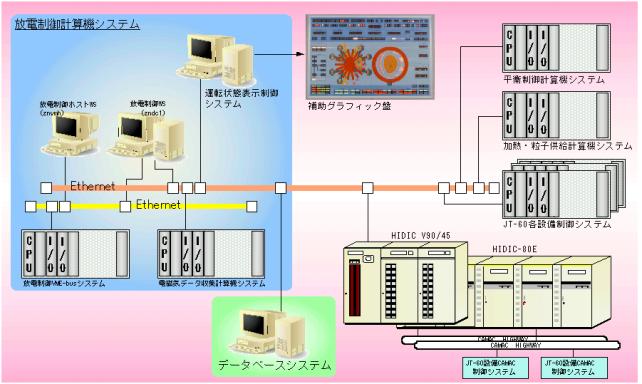

●放電制御計算機システム

放電制御計算機システムは、JT-60の実験放電を手順通りに実行させるための放電シーケンス制御を実行し、この放電シーケンス制御の中で設備制御計算機にさまざまな動作指令を出力する。また、放電条件の設定や放電シーケンスの監視、収集された実験データの参照を行い、JT-60の実験放電を進める役割を持っている。

本システムは、ワークステーションとVME-busシステムで構成され、従来のミニコンピュータの放電制御に係わる機能の全てを新システムに置き換えた。ただし、JT-60設備の中にはネットワーク化が遅れている設備があるため、これらの設備がネットワーク化されたときのことを予め準備すると共に、現状は旧放電制御計算機(HIDEC-80E)にCAMAC通信機能をのみを残し、CAMAC通信を行えるように対応した。

本システムを構成する主な各機器(システム)は以下の通りである。

(1)放電制御VME-busシステム

CPUモジュールとI/Oモジュールで構成されたボードコンピュータシステムである。ホスト計算機であるWSとEthernetで接続されている。CPUモジュールは、放電条件に従った放電シーケンスを実行し、シーケンスの進行に伴い発生するタイミング信号の入出力や各設備への信号出力等をI/Oモジュールにて行う。

(2)放電制御ワークステーション

放電制御WSは、放電制御VME-busシステムで実行される放電シーケンスに従い、ネットワーク接続された各設備とメッセージ交信を行うと共に、各設備から放電結果データを収集しデータベースシステムに送信する。また、放電シーケンスの実効に必要な放電条件の編集や各設備の運転状態を検査する演算処理を行い、その結果を放電シーケンスに通知する。さらにSVP(メッセージ交信用計算機)を介して運転制御計算機へ放電シーケンス状態の通知、運転系データの取得、運転系CAMACとのメッセージ交信を行う。

(3)運転状態表示(大型グラフィック盤)制御システム

JT-60中央制御室の補助グラフィック盤に、放電番号や放電前時間、その他の各種プラズマ実験パラメータや装置機器の運転情報を表示するために、表示制御専用パソコンを用いたシステムを構築した。

(4)電磁気データ収集計算機システム

放電制御計算機システムの更新に対応して、VME-busシステムを用いた電磁気データ収集計算機システムを開発した。

電磁気データ収集計算機システム

本システムは、放電条件により設定された電磁気検出器信号を入力するデジタル積分器(V/F変換器)のゲインを設定し、実験中に発生する磁場信号、中性子発生率(フィッションチェンバ)および硬X線線量のデータを収集するシステムである。

CAMAC規格で構成された旧システムは、以下の問題を抱えていた。

(1)CAMAC規格機器の老朽化により、本システムの保守・管理が今後困難になることが予想された。

(2)平衡制御計算機と重複して取得しているデータや、現状不使用となっているデータが多数あり、必要以上に大きな容量の結果データとなっていた。

(3)放電制御計算機がフィッションチェンバのデータ(電圧値)を受信後、中性子発生率[個/秒]に換算し、中性子発生量[個/Shot]を算出していることが、放電シーケンス終了遅延の1つの要因となっていた。

(4)CAMAC規格のADCモジュールの分解能は12bitであり、VME-bus規格の16bit-ADCジュールと比較して精度が低かった。

そこで、本システムをVME-bus規格の電子機器で構成した新システムへ更新し、放電制御計算機の負荷低減およびシステム全体の性能向上を実現した。

●高精度長時間デジタル積分器

【開発目標】

トカマク装置の電磁気計測で、実験炉ITERで想定される長時間放電においても適用できる低ドリフトの積分器を開発する。

【積分方式の選択】

アナログ積分方式:長時間放電→大容量のコンデンサーが必要→コンデンサーの漏れ電流が積分誤差となる。

【開発課題】

積分ドリフト等の積分誤差を最小限にする。

【対 策】

・信号ノイズによる回路内基準電圧の変動(ドリフト) → 放熱フィン+冷却ファン、基準電圧発生素子構成の工夫

・微小電圧入力による不感帯 → アナログ回路とデジタル回路の光絶縁、接地方式の最適化